集成電路設計中的關(guān)鍵材料與技術(shù)演進

集成電路(Integrated Circuit, IC)是現(xiàn)代信息技術(shù)的核心,其設計與制造離不開關(guān)鍵材料的支撐。本課件將系統(tǒng)介紹集成電路設計所涉及的主要材料體系、特性及其對設計的影響,并展望未來材料技術(shù)的發(fā)展趨勢。

一、集成電路設計概述與材料的基礎性作用

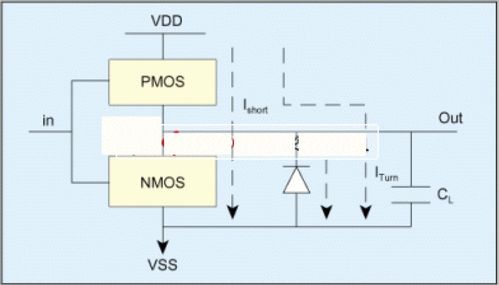

集成電路設計是將系統(tǒng)功能轉(zhuǎn)化為物理版圖的過程,涉及邏輯設計、電路設計、物理設計等多個層級。而材料的物理與化學特性——如硅的半導體性質(zhì)、二氧化硅的絕緣性、銅的低電阻率——從根本上決定了器件的性能、功耗、可靠性與集成度。材料是設計的物理承載,設計需求也反過來驅(qū)動材料創(chuàng)新。

二、核心材料體系及其在設計中的考量

- 襯底材料

- 硅(Si):絕對主流,成本、工藝成熟度、特性平衡最佳。設計需考慮其晶向、摻雜類型與濃度對載流子遷移率的影響。

- 化合物半導體(如GaAs、SiC、GaN):用于高頻、高壓、光電子等特殊領域。設計需適配其更高的電子遷移率或?qū)捊麕匦浴?/li>

- 絕緣體上硅(SOI):減少寄生電容,降低功耗,設計利于實現(xiàn)低功耗電路。

- 互連材料

- 傳統(tǒng)鋁(Al)互連:已被銅(Cu)替代。銅電阻率更低,減少RC延遲,但需設計阻擋層防止擴散。

- 新興互連材料:如鈷(Co)、釕(Ru)等,在先進節(jié)點用于局部互連,設計需應對新材料帶來的工藝整合挑戰(zhàn)。

- 介質(zhì)材料

- 柵氧化層:從二氧化硅(SiO?)到高介電常數(shù)(High-k)材料(如HfO?),允許物理厚度增加以減少漏電,同時維持電容,晶體管模型需相應更新。

- 層間介質(zhì)(ILD):從二氧化硅到低介電常數(shù)(Low-k)乃至超低介電常數(shù)材料,以降低互連線間的電容耦合和串擾,這對高速信號完整性的設計至關(guān)重要。

- 其他關(guān)鍵材料

- 金屬柵極:從多晶硅替換為金屬(如TiN),以解決High-k柵介質(zhì)下的柵耗盡問題,影響閾值電壓設計。

- 光刻膠與掩模版材料:決定圖形轉(zhuǎn)移的精度,直接關(guān)聯(lián)設計規(guī)則的最小線寬和套刻精度。

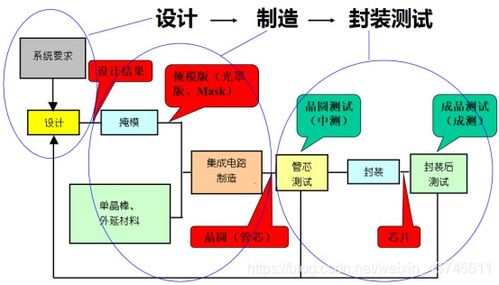

三、材料與設計流程的協(xié)同

- 設計規(guī)則(Design Rules):工藝廠提供的規(guī)則文件,本質(zhì)上是基于材料特性與工藝能力(如刻蝕、沉積)對物理版圖幾何尺寸、間距的約束。

- 工藝設計工具包(PDK):包含基于特定材料工藝的器件模型、符號、參數(shù)單元等,是設計與制造間的橋梁。

- 設計-工藝協(xié)同優(yōu)化(DTCO):在先進節(jié)點,設計與材料/工藝的互動更加緊密,需共同探索新材料(如二維材料、碳納米管)和新結(jié)構(gòu)(如GAA晶體管)下的設計方法學。

四、前沿材料趨勢與設計展望

- 三維集成與新材料:通過硅通孔(TSV)、混合鍵合等,實現(xiàn)芯片堆疊,涉及新型鍵合材料、介質(zhì)材料,推動從平面向三維的設計范式轉(zhuǎn)變。

- 超越硅基:二維材料(如石墨烯、二硫化鉬)、碳納米管等有望用于未來晶體管溝道,其獨特的電學特性將催生全新的器件架構(gòu)與電路設計。

- 異質(zhì)集成:將不同材料(如III-V族、硅光、壓電材料)制造的器件集成在同一芯片,實現(xiàn)更復雜系統(tǒng),要求設計工具和方法支持異質(zhì)兼容性。

集成電路設計并非孤立于材料的抽象過程。從硅片到最終封裝,每一步都建立在材料的物理現(xiàn)實之上。理解材料特性、跟蹤材料進展,是進行高效、創(chuàng)新集成電路設計的基礎。隨著摩爾定律的演進,新材料與新結(jié)構(gòu)的突破將成為推動集成電路性能持續(xù)提升的關(guān)鍵動力,也對設計人員提出了更高的跨學科知識要求。

如若轉(zhuǎn)載,請注明出處:http://www.11x98j.cn/product/89.html

更新時間:2026-04-12 05:36:12